## **Table of Contents**

| Welcome from the Chair4                   |

|-------------------------------------------|

| General Information5                      |

| Registration and Conference Store Hours 5 |

| Exhibit Hall Hours5                       |

| SC15 Information Booth/Hours5             |

| SC16 Preview Booth/Hours5                 |

| Social Events5                            |

| Registration Pass Access                  |

| SCinet 8                                  |

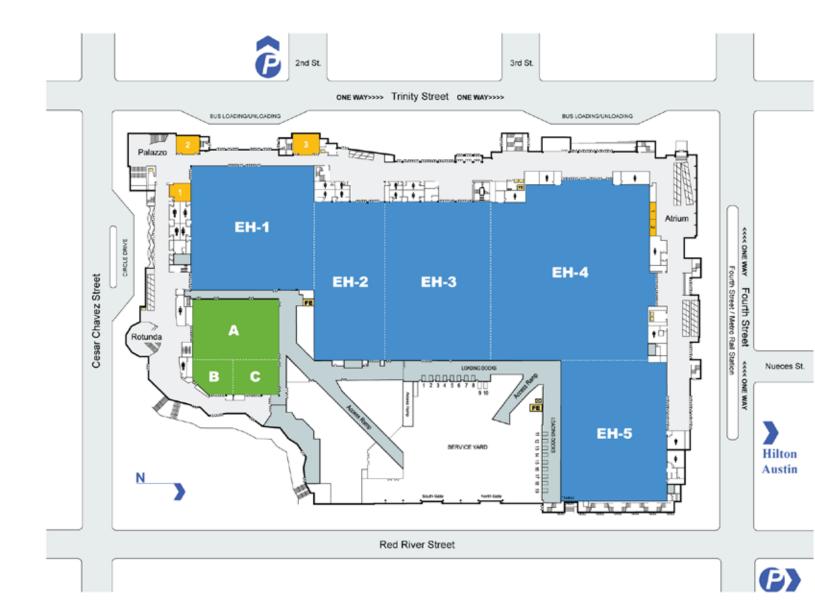

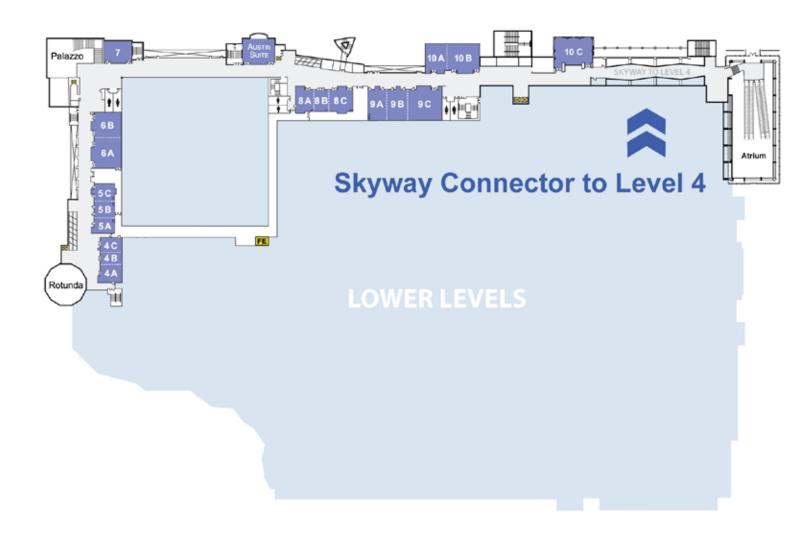

| Convention Center Maps 12                 |

| Daily Schedules                           |

| Plenary/Keynote/Invited Talks Plenary     |

| Awards Presentations33                    |

| Birds of a Feather36                      |

| Doctoral Showcase 50                      |

| Emerging Technologies54                   |

| Exhibitor Forums/57 HPC Impact Showcase   |

| Panels                                    |

| Papers                                                                            |

|-----------------------------------------------------------------------------------|

| Posters  Research Posters                                                         |

| Scientific Visualization/                                                         |

| Student Programs  Experiencing HPC for Undergraduates 122  Mentor-Protégé Program |

| Tutorials124                                                                      |

| Workshops                                                                         |

| Acknowledgements 153                                                              |

4 Welcome

### Welcome to SC15

Welcome to the fantastic city of Austin and to SC15, the International Conference for High Performance Computing, Networking, Storage and Analysis. With its vast technical community and the lively culture, Austin is a great place to host the 27th annual SC Conference.

HPC is transforming our everyday lives as well as our notso-ordinary ones---from nanomaterials to jet aircrafts, from medical treatments to disaster preparedness, and even the way we wash our clothes—the HPC community has transformed the world in multifaceted ways.

The technical program is going to be fantastic this year. We have a great Keynote lined up for you with Alan Alda speaking, as well as a variety of options including invited talks, papers, panel, and so much more. We are also launching a new initiative this year, the Early Career Program, which provides an opportunity for special sessions of interest to early career researchers, including getting funding, publishing venues, establishing long-term mentor relationships, and time management. The program is intended for people in their first five years of a permanent position (assistant professors and technical staff).

Don't forget to check out the HPC Matters Plenary with Diane Bryant from Intel. She will discuss how next-generation supercomputers are transforming HPC and presenting exciting opportunities to advance scientific research and discovery to deliver far-reaching impacts on society. After this session we will be opening the show floor. Come visit the over 300 exhibitors that are here to share with you the latest in our industry. They range from industry to academia and research and have something for everyone.

Make sure you also visit the SCinet booth to view the hardware that makes our network the best and fastest in the world. This is the 25th anniversary for SCinet as a component of the SC Conference series. This team is supporting the wireless network as well as the research network and the commodity network. Each year the SCinet NRE showcases a number of interesting network-based experiments during SC. This year they also took an initiative to bring more women into the SCinet community. Another positive change this year is that we have pulled all things related to students under one umbrella. Students@SC is focused on providing the next generation of HPC Community members with resources to help them grow. Amongst other things, they will be participating in the Mentor-Protégé program, a job fair, an educational dinner, the Student Cluster Competition and volunteering in critical positions throughout the week. Plus, they will have many other opportunities to network with interesting people.

There is literally too much for me to mention here, but if you need direction or just have a few questions, please stop by one of our two information booths.

Welcome to SC15 and to Austin, and I will see you in the Convention Center!

Jackie Kern

**SC General Chair**

**University of Illinois at Urbana-Champaign**

General Information 5

### **General Information**

#### **Registration and Conference Store**

The registration area and conference store are located in the Atrium of the Austin convention center.

#### **Registration/Conference Store Hours**

| Saturday, November 15  | 1pm-6pm    |

|------------------------|------------|

| Sunday, November 16    | 7am-6pm    |

| Monday, November 17    | 7am-9pm    |

| Tuesday, November 18   | 7:30am-6pm |

| Wednesday, November 19 | 7:30am-6pm |

| Thursday, November 20  | 7:30am-5pm |

| Friday, November 21    | 8am-11am   |

|                        |            |

#### **Registration Pass Access**

See page 7 for access grid.

#### **Exhibit Hall Hours**

| Tuesday, November 18   | 10am-6pm |

|------------------------|----------|

| Wednesday, November 19 | 10am-6pm |

| Thursday, November 20  | 10am-3pm |

#### **SC15 Information Booths**

Need up-to-the-minute information about what's happening at the conference. Need to know where to find your next session? What restaurants are close by? Where to get a document printed? These questions and more can be answered by a quick stop at one of the SC Information booths. There are two booth locations for your convenience: the main booth is located in the Fourth Street Concourse; the second booth is located at the Trinity Street Concourse.

Information Booth hours are as follows (note parentheses indicate hours for secondary booth; closed if no time indicated):

| Saturday, November 14       | 1pm-5pm            |

|-----------------------------|--------------------|

| Sunday, November 15         | 8am-6pm (8am-5pm)  |

| Monday November 16          | 8am-7pm (8am-5pm)  |

| <b>Tuesday November 17</b>  | 8am-6pm (10am-5pm) |

| Wednesday November 18       | 8am-6pm (8am-4pm)  |

| <b>Thursday November 19</b> | 8am-6pm            |

| Friday November 20          | 8:30am-12:30pm     |

#### **SC16 Preview Booth**

Members of next year's SC committee will be available in the SC16 preview booth (L12, located near the Fourth Street Entrance, outside Exhibit Hall 4) to offer information and discuss next year's SC conference in Salt Lake City, Utah. Stop by for a copy of next year's Call for Participation and pick up some free gifts!

The booth will be open during the following hours:

| Tuesday, Nov. 17   | 10am-6pm |

|--------------------|----------|

| Wednesday, Nov. 18 | 10am-6pm |

| Thursday, Nov. 19  | 10am-4pm |

#### **Social Events**

Exhibitors Reception Sunday, November 16 6pm-9pm Austin City Limits

The SC15 Exhibitors Reception will be held in the Moody Theater at Austin City Limits. The reception is open to all registered exhibitors. The reception is SC15's way of thanking exhibitors for their participation and support of the conference. The reception will feature a popular local band, The Spazmatics, access to all the memorabilia from 40 years of recording the Austin City Limits program at the theater, and a showcase of local food and drinks throughout the facility. Transportation will be provided from the bus loading area of the convention center starting at 5:45pm. An Exhibitor badge, party ticket and government-issued photo ID are required to attend this event.

### Exhibits Gala Opening Reception Monday, November 17 7pm-9pm

SC15 will host its annual Grand Opening Gala in the Exhibit Hall. This will be your first opportunity to see the latest high performance computing, networking, storage, analysis, and research products, services, and innovations. This event is open to all Technical Program, Exhibitors and Students@SC registrants.

6 General Information

Posters Reception Tuesday, November 18 5:15pm-7pm Level 4 - Concourse

The Posters Reception will located in the Concourse on Level 4 of the convention center. The reception is an opportunity for attendees to interact with poster presenters and includes research and ACM Student Research Competition posters. The reception is open to all attendees with Technical Program registration. Complimentary refreshments and appetizers will be available.

### Technical Program Conference Reception Thursday, November 19 6pm-9pm

The Darrell K Royal-Texas Memorial Stadium

Hook 'em Horns! SC15 will host a conference reception for all Technical Program attendees. Join us for a sporting good time at the Darrell K Royal-Texas Memorial Stadium, home to the UT Austin Longhorns football team. The stadium is the second largest stadium in the state of Texas, the ninth largest stadium in the United States, and the twelfth largest stadium in the world. Enjoy a warm Texas welcome from the UT Spirit Team and Bevo, the school mascot, a tour of the facility, delicious food and drink, music and much more. A Tech Program badge, event ticket, and government-issued photo ID are required to attend this event. Attendees are required to wear technical program badges throughout the reception, and badges may be checked during the event. Shuttle transportation to and from the event will run starting at 5:30pm from the convention center.

#### **Family Day**

Family Day is Wednesday, November 19, 4pm-6pm. Adults and children 12 and over are permitted on the floor during these hours when accompanied by a registered conference attendee.

#### **Lost Badge**

There is a \$40 processing fee to replace a lost badge.

#### **Facilities**

#### **Coat and Bag Check**

There are self-service locations for hanging coats within the Technical Program rooms and in the lobby. In addition, there is a coat and bag check on the premises.

#### **Parking**

There are two parking facilities at the Austin Convention Center:

- 10-story, 1,000-space garage located two blocks west of the facility, at Brazos and 210 East 2nd Street. Entrances on Brazos and San Jacinto streets.

- 5-story, 685-space garage located at the northeast corner of the facility at Red River and 4th Street. Entrances on Fifth Street.

#### First Aid/Emergency Medical Team

The Austin Convention Center will provide an onsite first aid room staffed with an emergency medical professional during the SC15 conference. The first aid room is located on the first level, north of the Trinity North Elevator. In the event of a medical or other emergency, attendees can dial 911 from any pay phone or dial 4111 from any house phone located in the facility. In addition, all uniformed security personnel are available to assist you in any emergency.

#### Wheelchair Accessibility

The Austin Convention Center complies with ADA requirements and is wheelchair accessible. Complimentary wheelchairs are available only for emergencies.

General Information 7

### **Registration Pass Access**

Each registration category provides access to a different set of conference activities, as summarized below.

| Summunized Delow.                                            |                      |                                     |           |                  |                                |                                  |

|--------------------------------------------------------------|----------------------|-------------------------------------|-----------|------------------|--------------------------------|----------------------------------|

| Type of Event                                                | Technical<br>Program | Technical<br>Program<br>+ Workshops | Tutorials | Workshop<br>Only | Exhibitor<br>24-hour<br>Access | Exhibit<br>Hall Only<br>Tue-Thur |

| Awards (Thursday)                                            | *                    | *                                   |           | *                | *                              | *                                |

| Birds-of-a-Feather                                           | *                    | *                                   |           | *                | *                              | *                                |

| Conference Reception (Thursday)                              | *                    | *                                   |           |                  |                                |                                  |

| Doctoral Showcase                                            | *                    | »j¢                                 |           |                  |                                |                                  |

| <b>Emerging Technologies</b>                                 | *                    | *                                   | *         | *                | *                              | *                                |

| Exhibit Floor                                                | *                    | *                                   |           |                  | *                              | *                                |

| Exhibitor Forum                                              | *                    | *                                   |           |                  | *                              | *                                |

| Exhibits Gala Opening (Monday)                               | *                    | *                                   |           |                  | *                              |                                  |

| Exhibitors Reception                                         |                      |                                     |           |                  | *                              |                                  |

| HPC Impact Showcase                                          | *                    | *                                   | *         | *                | *                              | *                                |

| HPC Matters Plenary (NO<br>BADGE REQUIRED/OPEN<br>TO PUBLIC) | *                    | *                                   | *         | ж                | *                              | *                                |

| Invited Talks (Non-<br>Plenary)                              | *                    | *                                   |           |                  |                                |                                  |

| Invited Talks (Plenary)                                      | *                    | *                                   |           |                  | *                              |                                  |

| Keynote (Tuesday)                                            | *                    | *                                   | *         | *                | *                              | *                                |

| Panels (Tue-Thur)                                            | *                    | *                                   |           |                  |                                |                                  |

| Panels (Friday Only)                                         | *                    | *                                   |           |                  | *                              | *                                |

| Papers                                                       | *                    | *                                   |           |                  |                                |                                  |

| Posters                                                      | *                    | aje                                 |           |                  | *                              | *                                |

| Poster Reception<br>(Tuesday)                                | *                    | *                                   |           |                  |                                |                                  |

| Scientific Visualization<br>Showcase                         | *                    | *                                   |           |                  |                                |                                  |

| Tutorial Lunch (Sun/Mon ONLY)                                |                      |                                     | *         |                  |                                |                                  |

| <b>Tutorial Sessions</b>                                     |                      |                                     | *         |                  |                                |                                  |

| Students@SC                                                  | *                    | *                                   | *         |                  | *                              | *                                |

| Student Cluster<br>Competition                               | *                    | *                                   |           |                  | *                              |                                  |

| Workshops                                                    |                      | *                                   |           | *                |                                |                                  |

### **SCinet**

#### **The Fastest Network Connecting the Fastest Computers**

SC15 is once again hosting one of the most powerful and advanced networks in the world - SCinet. Created each year for the conference, SCinet brings to life a very high-capacity network that supports the revolutionary applications and experiments that are a hallmark of the SC conference. SCinet will link the convention center to research and commercial networks around the world. In doing so, SCinet serves as the platform for exhibitors to demonstrate the advanced computing resources of their home institutions and elsewhere by supporting a wide variety of bandwidth-driven applications including supercomputing and cloud computing.

Volunteers from academia, government and industry work together to design and deliver the SCinet infrastructure. Industry vendors and carriers donate millions of dollars in equipment and services needed to build the local and wide area networks. Planning begins more than a year in advance of each SC conference and culminates in a high-intensity installation in the days leading up to the conference.

For SC15, SCinet is exploring up-and-coming topics in the high-performance networking community of SC through the Network Research Exhibition (NRE) and returning from its inaugural appearance in 2014, the INDIS workshop.

In addition, SCinet has created a new Diversity Program, funded by the NSF, to fund U.S. women in their early to mid careers to participate in SCinet to get hands-on training and build their professional network.

#### **SCinet Network Research Exhibition (NRE)**

The NRE is SCinet's forum for displaying new or innovative demonstrations in network testbeds, emerging network hardware, protocols, and advanced network intensive scientific applications that will stretch the boundaries of a high-performance network.

### **SCinet INDIS Workshop**

The second annual INDIS workshop is again part of the Technical Program. Innovating the Network for Data-Intensive Science (INDIS) showcases both demonstrations and technical papers highlighting important developments in high-performance networking. With participants from research, industry, and government, this workshop will discuss topics related to network testbeds, emerging network hardware, protocols, and advanced network-intensive scientific applications.

**SCinet Collaborators** 9

### **SCinet Collaborators**

SCinet is the result of the hard work and significant contributions of many government, research, education and corporate collaborators. Collaborators for SC15 include:

### **Platinum**

Gold

10 SCinet Collaborators

### **SCinet Collaborators**

### Silver

### **Reservoir** Labs

SCinet Collaborators 11

### **SCinet Collaborators**

### **Bronze**

1

### **MULTI-LEVEL FLOOR PLAN DETAIL**

2

### **MEZZANINES AND SHOW OFFICES**

## 3

### **LEVEL 3 MEETING ROOMS**

### LEVEL 4 GRAND BALLROOM, MEETING ROOMS

### **SATURDAY, NOVEMBER 14**

| Time    | Event Type  | Session Title       | LocationTime |

|---------|-------------|---------------------|--------------|

| 5pm-6pm | Students@SC | Program Orientation | 9BC          |

### **SUNDAY, NOVEMBER 15**

| SUNDAI, IN  | OVEWBER 15  |                                                                           |                |

|-------------|-------------|---------------------------------------------------------------------------|----------------|

| Time        | Event Type  | Session Title                                                             | LocationTime   |

| 8:30am-10am | Students@SC | Why SC, HPC and Computer Science Need Diversity                           | 9BC            |

| 8:30am-12pm | Tutorial    | Architecting, Implementing and Supporting Multi-Level Security            | 18A            |

|             |             | Ecosystem in HPC, ISR, Big Data Analysis and Other Environments           |                |

| 8:30am-12pm | Tutorial    | Benchmarking Platforms for Large-Scale Graph Processing and               | 19B            |

|             |             | RDF Data Management: The LDBC Approach                                    |                |

| 8:30am-12pm | Tutorial    | Data-Intensive Applications on HPC Using Hadoop, Spark and                | 18C            |

|             |             | RADICAL Cybertools                                                        |                |

| 8:30am-12pm | Tutorial    | Large-Scale Visualization with ParaView                                   | 13AB           |

| 8:30am-12pm | Tutorial    | MPI+X—Hybrid Programming on Modern Compute Clusters with                  | 16AB           |

|             |             | Multicore Processors and Accelerators                                     |                |

| 8:30am-12pm | Tutorial    | Automatic Performance and Energy Tuning with the Periscope                | 19A            |

|             |             | Tuning Framework                                                          |                |

| 8:30am-5pm  | Tutorial    | Introduction to OpenMP                                                    | 17B            |

| 8:30am-5pm  | Tutorial    | Efficient Parallel Debugging for MPI, Threads and Beyond                  | 14             |

| 8:30am-5pm  | Tutorial    | Fault-Tolerance for HPC: Theory and Practice                              | 18D            |

| 8:30am-5pm  | Tutorial    | Linear Algebra Libraries for HPC: Scientific Computing with Multicore and | 15             |

|             |             | Accelerators                                                              |                |

| 8:30am-5pm  | Tutorial    | Massively Parallel Task-Based Programming with HPX                        | 17A            |

| 8:30am-5pm  | Tutorial    | Parallel Computing 101                                                    | 18B            |

| 8:30am-5pm  | Tutorial    | Parallel I/O in Practice                                                  | 12A            |

| 8:30am-5pm  | Tutorial    | Parallel Programming in Modern Fortran                                    | 12B            |

| 9am-12:30pm | Workshop    | Computational and Data Challenges in                                      | Hilton 406     |

|             |             | Genomic Sequencing                                                        |                |

| 9am-12:30pm | Workshop    | First International Workshop on Heterogeneous Computing with              | Hilton Salon D |

|             |             | Reconfigurable Logic                                                      |                |

| 9am-12:30pm | Workshop    | Portability Among HPC Architectures for Scientific Applications           | Hilton Salon G |

| 9am-5:30pm  | Workshop    | DISCS2015: International Workshop on Data Intensive Scalable              | Hilton Salon J |

|             |             | Computing Systems                                                         |                |

| 9am-5:30pm  | Workshop    | E2SC2015: Energy Efficient Super Computing                                | Hilton Salon F |

| 9am-5:30pm  | Workshop    | ESPM2: First International Workshop on Extreme                            | Hilton 410     |

|             |             | Scale Programming Models&Middleware                                       |                |

| 9am-5:30pm  | Workshop    | IA^3 2015: Fifth Workshop on Irregular                                    | Hilton Salon A |

|             |             | Applications: Architecture and Algorithms                                 |                |

| 9am-5:30pm  | Workshop    | LLVM-HPC2015: Second Workshop on the LLVM Compiler                        | Hilton Salon E |

|             |             | Infrastructure in HPC                                                     |                |

|             |             |                                                                           |                |

### **SUNDAY, NOVEMBER 15**

| Time          | Event Type   | Session Title                                                               | LocationTime       |

|---------------|--------------|-----------------------------------------------------------------------------|--------------------|

| 9am-5:30pm    | Workshop     | PMBS2015: Sixth International Workshop on Performance Modeling,             | Hilton Salon K     |

|               |              | Benchmarking, and Simulation of HPC Systems                                 |                    |

| 9am-5:30pm    | Workshop     | PyHPC2015: Fifth Workshop on Python for High-Performance and                | Hilton Salon C     |

|               |              | Scientific Computing                                                        |                    |

| 9am-5:30pm    | Workshop     | The Sixth International Workshop on Data-Intensive Computing                | Hilton 412         |

|               |              | in the Clouds                                                               |                    |

| 9am-5:30pm    | Workshop     | VISTech Workshop 2015: Visualization Infrastructure and                     | Hilton Salon B     |

|               |              | Systems Technology                                                          |                    |

| 9am-5:30pm    | Workshop     | WORKS2015: Tenth Workshop on Workflows in Support of Large-Scale Science    | Hilton 408         |

| 10am-10:30am  | Tutorial     | Refreshment Break                                                           | Level 4 - Lobby    |

| 10am-10:30am  | Workshop     | Refreshment Break                                                           | Hilton 4th Floor   |

| 10:30am-12pm  | Students@SC  | Diversity Panel: Collective Responsibilities for Biases, Micro-aggressions, | 9BC                |

|               |              | Isolation and More                                                          |                    |

| 12pm-1:30pm   | Tutorial     | Lunch                                                                       | Ballroom DEFG      |

| 1:30pm-3pm    | Students@SC  | Education Panel: Making the Most of Graduate School (in HPC)                | 9BC                |

| 1:30pm-5pm    | Tutorial     | Effective HPC Visualization and Data Analysis using VisIt                   | 18C                |

| 1:30pm-5pm    | Tutorial     | Insightful Automatic Performance Modeling                                   | 18A                |

| 1:30pm-5pm    | Tutorial     | Live Programming: Bringing the HPC Development Workflow to Life             | 16AB               |

| 1:30pm-5pm    | Tutorial     | Power Aware HPC: Challenges and Opportunities for Application Developers    | 19A                |

| 1:30pm-5pm    | Tutorial     | Productive Programming in Chapel: A Computation-Driven Introduction         | 19B                |

| 1:30pm-5pm    | Tutorial     | Towards Comprehensive System Comparison: Using the SPEC HPG                 | 13AB               |

|               |              | Benchmarks HPC Systems for Better Analysis, Evaluation, and Procurement     |                    |

|               |              | of Next-Generation                                                          |                    |

| 2:00pm-5:30pm | Workshop     | Computational Approaches for Cancer                                         | Hilton 406         |

| 2:00pm-5:30pm | Workshop     | Many-Task Computing on Clouds, Grids and Supercomputers                     | Hilton Salon G     |

| 2:00pm-5:30pm | Workshop     | MLHPC2015: Machine Learning in HPC Environments                             | Hilton Salon D     |

| 3pm-3:30pm    | Tutorial     | Refreshment Break                                                           | Level 4 - Lobby    |

| 3pm-3:30pm    | Workshop     | Refreshment Break                                                           | Hilton 4th Floor   |

| 3:30pm-5pm    | Students@SC  | Career Panel: Outlooks and Opportunities from Academia, Industry and        | 9BC                |

|               |              | Research Labs                                                               |                    |

| 6pm-8pm       | Students@SC  | Dinner                                                                      | Ballroom G         |

| 6pm-9pm       | Social Event | Exhibitor Reception                                                         | Austin City Limits |

|               |              | (Exhibitor badge required for access)                                       |                    |

### **MONDAY, NOVEMBER 16**

| Time        | Event Type  | Session Title                                                                  | LocationTime   |

|-------------|-------------|--------------------------------------------------------------------------------|----------------|

| 8:30am-10am | Students@SC | Research Panel: A Best Practices Guide to (HPC) Research                       | 9BC            |

| 8:30am-10am | Tutorial    | From Description to Code Generation: Building High-Performance                 | 17A            |

|             |             | Tools in Python                                                                |                |

| 8:30am-12pm | Tutorial    | Getting Started with In Situ Analysis and Visualization Using ParaView Catalys | 12B            |

| 8:30am-12pm | Tutorial    | InfiniBand and High-Speed Ethernet for Dummies                                 | 16AB           |

| 8:30am-12pm | Tutorial    | Managing Data Throughout the Research                                          | 15             |

|             |             | Lifecycle Using Globus Software-as-a-Service                                   |                |

| 8:30am-12pm | Tutorial    | MCDRAM (High Bandwidth Memory) on Knights Landing—                             | 18A            |

|             |             | Analysis Methods/Tools                                                         |                |

| 8:30am-12pm | Tutorial    | Practical Fault Tolerance on Today's HPC Systems                               | 18D            |

| 8:30am-12pm | Tutorial    | Practical Hybrid Parallel Application Performance Engineering                  | 14             |

| 8:30am-5pm  | Tutorial    | Advanced MPI Programming                                                       | 18B            |

| 8:30am-5pm  | Tutorial    | Advanced OpenMP: Performance and 4.1 Features                                  | 13AB           |

| 8:30am-5pm  | Tutorial    | How to Analyze the Performance of Parallel Codes 101                           | 19A            |

| 8:30am-5pm  | Tutorial    | Node-Level Performance Engineering                                             | 18C            |

| 8:30am-5pm  | Tutorial    | OpenACC Programming For Accelerators                                           | 12A            |

| 8:30am-5pm  | Tutorial    | Portable Programs for Heterogeneous Computing:                                 | 17B            |

|             |             | A Hands-On Introduction                                                        |                |

| 8:30am-5pm  | Tutorial    | Programming the Xeon Phi                                                       | 19B            |

| 9am-12:30pm | Workshop    | INDIS-15: The Second Workshop on Innovating the                                | Hilton 410     |

|             |             | Network for Data Intensive Science                                             |                |

| 9am-12:30pm | Workshop    | Second SC Workshop on Best Practices for HPC Training                          | Hilton Salon K |

| 9am-12:30pm | Workshop    | Ultravis '15: The Tenth Workshop on Ultrascale Visualization                   | Hilton Salon D |

| 9am-5:30pm  | Workshop    | ATIP Workshop on Chinese HPC Research Toward                                   | Hilton 412     |

|             |             | New Platforms and Real Applications                                            |                |

| 9am-5:30pm  | Workshop    | Co-HPC2015: Second International Workshop on Hardware-Software                 | Hilton Salon C |

|             |             | Co-Design for HPC                                                              |                |

| 9am-5:30pm  | Workshop    | ESPT2015: Extreme-Scale Programming Tools                                      | Hilton Salon B |

| 9am-5:30pm  | Workshop    | ExaMPI15: Workshop on Exascale MPI                                             | Hilton Salon F |

| 9am-5:30pm  | Workshop    | PDSW10 2015: Tenth Workshop on Parallel                                        | Hilton Salon G |

|             |             | Data Storage                                                                   |                |

| 9am-5:30pm  | Workshop    | Runtime Systems for Extreme Scale Programming Models &                         | Hilton 400-402 |

|             |             | Architectures (RESPA)                                                          |                |

| 9am-5:30pm  | Workshop    | SCalA15: Sixth Workshop on Latest Advances in                                  | Hilton Salon E |

|             |             | Scalable Algorithms for Large-Scale Systems                                    |                |

| 9am-5:30pm  | Workshop    | Sixth Annual Workshop for the Energy Efficient                                 | Hilton Salon A |

|             |             | HPC Working Group (EE HPC WG)                                                  |                |

| 9am-5:30pm  | Workshop    | Sixth SC Workshop on Big Data Analytics: Challenges and                        | Hilton Salon J |

|             |             | Opportunities (BDAC-15)                                                        |                |

|             |             |                                                                                |                |

### **MONDAY, NOVEMBER 16**

| Time          | Event Type              | Session Title                                                                | LocationTime     |

|---------------|-------------------------|------------------------------------------------------------------------------|------------------|

| 9am-5:30pm    | Workshop                | WACCPD: Workshop on Accelerator Programming Using Directives                 | Hilton 406       |

| 9am-5:30pm    | Workshop                | WOLFHPC15: Fifth International Workshop on                                   | Hilton 408       |

|               |                         | Domain-Specific Languages and High-Level Frameworks for HPC                  |                  |

| 10am-10:30am  | Tutorial                | Refreshment Break                                                            | Level 4 -Lobby   |

| 10am-10:30am  | Workshop                | Refreshment Break                                                            | Hilton 4th Floor |

| 10:30am-12pm  | Students@SC             | What's at SC?                                                                | 9BC              |

| 12pm-1:30pm   | Tutorial                | Lunch                                                                        | Ballroom DEFG    |

| 1:30pm-3pm    | Students@SC             | Peer Speed Meetings                                                          | 9ABC             |

| 1:30pm-5pm    | Tutorial                | Accelerating Big Data Processing with Hadoop, Spark and Memcached            | 16AB             |

|               |                         | on Modern Clusters                                                           |                  |

| 1:30pm-5pm    | Tutorial                | An Introduction to the OpenFabrics Interface API                             | 12B              |

| 1:30pm-5pm    | Tutorial                | Data Management, Analysis and Visualization Tools for Data-Intensive Science | 17A              |

| 1:30pm-5pm    | Tutorial                | Debugging and Performance Tools for MPI and OpenMP 4.0 Applications          | 14               |

|               |                         | for CPU andAccelerators/Coprocessors                                         |                  |

| 1:30pm-5pm    | Tutorial                | Getting Started with Vector Programming using AVX-512 on Multicore and       | 15               |

|               |                         | Many-Core Platforms                                                          |                  |

| 1:30pm-5pm    | Tutorial                | Kokkos: Enabling Manycore Performance Portability for C++ Applications       | 18D              |

|               |                         | and Domain Specific Libraries/Languages                                      |                  |

| 1:30pm-5pm    | Tutorial                | Measuring the Power/Energy of Modern Hardware                                | 18A              |

| 2:00pm-5:30pm | Workshop                | EduHPC2015: Workshop on Education for HPC                                    | Hilton Salon K   |

| 2:00pm-5:30pm | Workshop                | ISAV2015: First Workshop on In Situ Infrastructures for Enabling             | Hilton Salon D   |

|               |                         | Extreme-Scale Analysis and Visualization                                     |                  |

| 2:00pm-5:30pm | Workshop                | NDM-15: Fifth International Workshop on Network-Aware                        | Hilton 410       |

|               |                         | Data Management                                                              |                  |

| 3pm-3:30pm    | Tutorial                | Refreshment Break                                                            | Level 4 -Lobby   |

| 3pm-3:30pm    | Workshop                | Refreshment Break                                                            | Hilton 4th Floor |

| 3pm-5pm       | HPC for Undergraduates  | Orientation                                                                  | Hilton 404       |

| 3:30pm-5pm    | Students@SC             | Mentor-Protégé Mixer                                                         | 9ABC             |

| 5pm-11:55pm   | SCC                     | Student Cluster Competition Kickoff                                          | Palazzo          |

| 5:30pm-6:30pm | Keynote & Plenary Talks | HPC Matters Plenary (Diane Bryant)                                           | Ballroom DEFG    |

| 7pm-9pm       | Social Event            | Gala Opening Reception                                                       | Exhibit Hall     |

|               |                         |                                                                              |                  |

### **TUESDAY, NOVEMBER 17**

| I OLODAI,       | NOVEMBER 17             |                                                                        |                 |

|-----------------|-------------------------|------------------------------------------------------------------------|-----------------|

| Time            | Event Type              | Session Title                                                          | Location        |

| 6am-11:55pm     | Students@SC             | Student Cluster Competition                                            | Palazzo         |

| 8:30am-10am     | Keynote & Plenary Talks | Keynote - Mr. Alan Alda - Getting Beyond a Blind Date with Science:    | Ballroom DEFG   |

|                 |                         | Communicating Science for Scientists                                   |                 |

| 8:30am-5pm      | Posters                 | Research Posters ACM Student Research                                  | Level 4 - Lobby |

|                 |                         | Competition Posters                                                    |                 |

| 9am-5:30pm      | Emerging Technologies   | Emerging Technologies Exhibits                                         | 14              |

| 10am-10:30am    | Tech Program            | Refreshment Break                                                      | Level 4 - Lobby |

| 10:30am-11:30am | Paper                   | Data Clustering                                                        | 18CD            |

| 10:30am-12pm    | Paper                   | Applications: Material Science                                         | 18AB            |

| 10:30am-12pm    | Paper                   | Cache and Memory Subsystems                                            | 19AB            |

| 10:30am-12pm    | Birds of a Feather      | HDF5: State of the Union                                               | 13A             |

| 10:30am-12pm    | Birds of a Feather      | Lustre Community BOF: Enabling Big Data with Lustre                    | 15              |

| 10:30am-12pm    | Birds of a Feather      | Planning for Visualization on the Xeon Phi                             | 13B             |

| 10:30am-12pm    | Exhibitor Forum         | HPC Futures and Exascale                                               | 12AB            |

| 10:30am-12pm    | HPC for Undergraduates  | Introduction to HPC Research                                           | Hilton 404      |

| 10:30am-12pm    | Invited Talks           | Invited Talks Session 1                                                | Ballroom DEFG   |

| 12:15pm-1:15pm  | Birds of a Feather      | Eleventh Graph500 List                                                 | 18CD            |

| 12:15pm-1:15pm  | Birds of a Feather      | Getting Scientific Software Installed: Tools and                       | 19AB            |

|                 |                         | Best Practices                                                         |                 |

| 12:15pm-1:15pm  | Birds of a Feather      | Integrating Data Commons and Other Data Infrastructure with HPC to     | 15              |

|                 |                         | Infrastructure with HPC to Research and Discovery                      |                 |

| 12:15pm-1:15pm  | Birds of a Feather      | Operating System and Runtime for Exascale                              | 17AB            |

| 12:15pm-1:15pm  | Birds of a Feather      | SAGE2: Scalable Amplified Group Environment for Global Collaboration   | 13A             |

|                 |                         | Global Collaboration                                                   |                 |

| 12:15pm-1:15pm  | Birds of a Feather      | The Challenge of A Billion Billion Calculations per Second: InfiniBand | 18AB            |

|                 |                         | Roadmap Shows the Future of the High Performance Standard Interconnect |                 |

|                 |                         | for Exascale Programs                                                  |                 |

| 12:15pm-1:15pm  | Birds of a Feather      | OpenSHMEM: User Experience, Tool Ecosystem, Version 1.2 and Beyond     | 13B             |

| 12:15pm-1:15pm  | Birds of a Feather      | SIGHPC Annual Meeting                                                  | 16AB            |

| 1:00pm-3:30pm   | HPC Impact Showcase     | HPC Impact Showcase - Tuesday                                          | 12AB            |

| 1:30pm-2:15pm   | Award Presentations     | SC15 Test of Time Award Special Lecture                                | Ballroom D      |

| 1:30pm-3pm      | Birds of a Feather      | Advancing the State of the Art in Network APIs -                       | 13A             |

|                 |                         | The OpenFabrics Interface APIs                                         |                 |

| 1:30pm-3pm      | Birds of a Feather      | Understanding User-Level Activity on Today's Supercomputers with XALT  | 13B             |

| 1:30pm-3pm      | Birds of a Feather      | Virtualization and Clouds in HPC: Motivation, Challenges and           | 15              |

|                 |                         | Lessons Learned                                                        |                 |

| 1:30pm-3pm      | Panel                   | Post Moore's Law Computing: Digital versus Neuromorphic                | 16AB            |

|                 |                         | versus Quantum                                                         |                 |

| 1:30pm-3pm      | Paper                   | Applications: Biophysics and Genomics                                  | 18AB            |

|                 |                         |                                                                        |                 |

### **TUESDAY, NOVEMBER 17**

| Time       | Event Type         | Session Title                                                           | Location        |

|------------|--------------------|-------------------------------------------------------------------------|-----------------|

| 1:30pm-3pm | Paper              | GPU Memory Management                                                   | 19AB            |

| 1:30pm-3pm | Paper              | Scalable Storage Systems                                                | 18CD            |

| 3pm-3:30pm | Tech Program       | Refreshment Break                                                       | Level 4 - Lobby |

| 3:30pm-5pm | Paper              | Applications: Folding, Imaging and Proteins                             | 18AB            |

| 3:30pm-5pm | Paper              | Graph Analytics on HPC Systems                                          | 19AB            |

| 3:30pm-5pm | Paper              | MPI/Communication                                                       | 18CD            |

| 3:30pm-5pm | Birds of a Feather | Characterizing Extreme-Scale Computational and                          | 13A             |

|            |                    | Data-Intensive Workflows                                                |                 |

| 3:30pm-5pm | Birds of a Feather | Performance Reproducibility in HPC -                                    | 13B             |

|            |                    | Challenges and State-of-the-Art                                         |                 |

| 3:30pm-5pm | Birds of a Feather | UCX - Communication Framework for Exascale                              | 15              |

|            |                    | Programming Environments                                                |                 |

| 3:30pm-5pm | Invited Talks      | Invited Talks Session 2                                                 | Ballroom D      |

| 3:30pm-5pm | Panel              | Future of Memory Technology for Exascale and Beyond III                 | 16AB            |

|            |                    | Beyond III                                                              |                 |

| 3:30pm-5pm | Exhibitor Forum    | Hardware and Architecture                                               | 12AB            |

| 5:15pm-7pm | Posters Reception  | Research & ACM SRC Poster Reception                                     | Level 4 - Lobby |

| 5:30pm-7pm | Birds of a Feather | Dynamic Liquid Cooling, Telemetry and Controls:                         | 18CD            |

|            |                    | Opportunity for Improved TCO?                                           |                 |

| 5:30pm-7pm | Birds of a Feather | Interactivity in Supercomputing                                         | 19AB            |

| 5:30pm-7pm | Birds of a Feather | Maximizing Job Performance, Predictability and Manageability with Torqu | ıe 6.0 13A      |

| 5:30pm-7pm | Birds of a Feather | MPICH: A High-Performance Open-Source MPI Implementation                | 17AB            |

| 5:30pm-7pm | Birds of a Feather | OpenMP: Where are We and What's Next?                                   | 18AB            |

| 5:30pm-7pm | Birds of a Feather | Reconfigurable Supercomputing                                           | 16AB            |

| 5:30pm-7pm | Birds of a Feather | Strategies for Academic HPC Centers                                     | 15              |

| 5:30pm-7pm | Birds of a Feather | The Future of File Systems and Benchmarking, or Where Are We Going      | 13B             |

|            |                    | and How Do We Know We Got There?                                        |                 |

| 5:30pm-7pm | Birds of a Feather | TOP500 Supercomputers                                                   | Ballroom D      |

|            |                    |                                                                         |                 |

### **WEDNESDAY, NOVEMBER 18**

| Time           | Event Type               | Session Title                                                             | Location        |

|----------------|--------------------------|---------------------------------------------------------------------------|-----------------|

| 8:30am-10am    | Keynote & Plenary Talks  | Cray/Fernbach/Kennedy Award Recipients Talks                              | Ballroom D      |

| 8:30am-5pm     | Posters                  | Research and ACM SRC Posters                                              | Level 4 - Lobby |

| 9am-5:30pm     | Emerging Technologies    | Emerging Technologies Exhibits                                            | 14              |

| 10am-10:30am   | Tech Program             | Refreshment Break                                                         | Level 4 - Lobby |

| 10am-3pm       | Students@SC              | Student-Postdoc Job & Opportunity Fair                                    | 9ABC            |

| 10:30am-12pm   | Awards Presentations     | ACM Gordon Bell Finalists I                                               | 17AB            |

| 10:30am-12pm   | Exhibitor Forum          | Effective Application of HPC                                              | 12AB            |

| 10:30am-12pm   | HPC for Undergraduates   | Graduate Student Perspective                                              | Hilton 404      |

| 10:30am-12pm   | Invited Talks            | Invited Talks Session 3                                                   | Ballroom D      |

| 10:30am-12pm   | Panel                    | Supercomputing and Big Data: From Collision to Convergence                | 16AB            |

| 10:30am-12pm   | Paper                    | Cloud Resource Management                                                 | 19AB            |

| 10:30am-12pm   | Paper                    | Interconnection Networks                                                  | 18CD            |

| 10:30am-12pm   | Paper                    | State of the Practice: Infrastructure Management                          | 18AB            |

| 10:30am-12pm   | Birds of a Feather       | Big Data and Exascale Computing (BDEC) Community Report                   | 15              |

| 10:30am-12pm   | Birds of a Feather       | Connecting HPC and High Performance Networks for Scientists               | 13A             |

| 40.00          | D. I. ( E .I.            | and Researchers                                                           | 100             |

| 10:30am-12pm   | Birds of a Feather       | Women in HPC: Pathways and Roadblocks                                     | 13B             |

| 10:30am-12pm   | SCi Vis & Data Analytics | Scientific Visualization & Data Analytics Showcase                        | Ballroom E      |

| 12:15pm-1:15pm | Birds of a Feather       | Collaborative Paradigms for Developing HPC in Constrained<br>Environments | 17AB            |

| 12:15pm-1:15pm | Birds of a Feather       | Fresco: An Open Failure Data Repository for Dependability                 | Ballroom G      |

|                |                          | Research and Practice                                                     |                 |

| 12:15pm-1:15pm | Birds of a Feather       | HPC Education: Meeting of the SIGHPC Education Chapter                    | 15              |

| 12:15pm-1:15pm | Birds of a Feather       | Migrating Legacy Applications to Emerging Hardware                        | 16AB            |

| 12:15pm-1:15pm | Birds of a Feather       | Oil & Gas Community: Enabling FWI for Exascale                            | 13A             |

| 12:15pm-1:15pm | Birds of a Feather       | Open MPI State of the Union                                               | 18CD            |

| 12:15pm-1:15pm | Birds of a Feather       | QuantumChemistry500                                                       | 13B             |

| 12:15pm-1:15pm | Birds of a Feather       | The 2015 Ethernet Roadmap - Are We to Terabit Ethernet Yet?               | 19A             |

| 12:15pm-1:15pm | Birds of a Feather       | The Open Community Runtime (OCR) Framework for Extreme                    | 18AB            |

|                |                          | Scale Systems                                                             |                 |

| 12:15pm-1:15pm | Birds of a Feather       | The Partitioned Global Address Space (PGAS) Model                         | Ballroom F      |

| 1:00pm-3:30pm  | HPC Impact Showcase      | HPC Impact Showcase - Wednesday                                           | 12AB            |

| 1:30pm-3pm     | Birds of a Feather       | HPC 2020 in the BioPharma Industry                                        | 13A             |

| 1:30pm-3pm     | Birds of a Feather       | HPCG Benchmark Update                                                     | 15              |

| 1:30pm-3pm     | Birds of a Feather       | Supercomputing After the End of Moore's Law                               | 13B             |

| 1:30pm-3pm     | Invited Talks            | Invited Talks Session 4                                                   | Ballroom D      |

| 1:30pm-3pm     | Panel                    | Mentoring Undergraduates Through Competition                              | 16AB            |

| 1:30pm-3pm     | Paper                    | Applications: Climate and Weather                                         | 18CD            |

| 1:30pm-3pm     | Paper                    | Data Transfers and Data Intensive Applications                            | 19AB            |

| 1:30pm-3pm     | Paper                    | Performance Tools and Models                                              | 18AB            |

| <br>           |                          |                                                                           |                 |

### **WEDNESDAY, NOVEMBER 18**

| Time          | Event Type         | Session Title                                                      | Location        |

|---------------|--------------------|--------------------------------------------------------------------|-----------------|

| 3pm-3:30pm    | Tech Program       | Refreshment Break                                                  | Level 4 - Lobby |

| 3:30pm-5pm    | Exhibitor Forum    | Software for HPC                                                   | 12AB            |

| 3:30pm-5pm    | Invited Talks      | Invited Talks Session 5                                            | Ballroom D      |

| 3:30pm-5pm    | Panel              | Programming Models for Parallel Architectures                      | 16AB            |

|               |                    | and Requirements for Pre-Exascale                                  |                 |

| 3:30pm-5pm    | Paper              | In Situ (Simulation Time) Analysis                                 | 18CD            |

| 3:30pm-5pm    | Paper              | Linear Algebra                                                     | 18AB            |

| 3:30pm-5pm    | Paper              | Management of Graph Workloads                                      | 19AB            |

| 3:30pm-5pm    | Birds of a Feather | Fault Tolerant MPI Applications with ULFM                          | 13A             |

| 3:30pm-5pm    | Birds of a Feather | The Message Passing Interface: MPI 3.1 Released, Next Stop MPI 4.0 | 15              |

| 3:30pm-5:15pm | ACM SRC            | ACM SRC Poster Presentations                                       | 17AB            |

| 4pm-6pm       | Family Day         | Registered Attendee with Children ages 12+                         | Exhibit Hall    |

| 5pm-6pm       | SCC                | Student Cluster Competition Finale                                 | Palazzo         |

| 5pm-6pm       | Students@SC        | Social Hour with Interesting People                                | 9ABC            |

| 5:30pm-7pm    | Birds of a Feather | America's HPC Collaboration                                        | Hilton 404      |

| 5:30pm-7pm    | Birds of a Feather | Ceph in HPC Environments                                           | Hilton 406      |

| 5:30pm-7pm    | Birds of a Feather | Challenges in Managing Small HPC Centers                           | 15              |

| 5:30pm-7pm    | Birds of a Feather | Flocking Together: Experience the Diverse                          | 17AB            |

|               |                    | OpenCL Ecosystem                                                   |                 |

| 5:30pm-7pm    | Birds of a Feather | High Performance Geometric Multigrid (HPGMG):                      | 18CD            |

|               |                    | an HPC Benchmark for Modern Architectures and                      |                 |

|               |                    | Metric for Machine Ranking                                         |                 |

| 5:30pm-7pm    | Birds of a Feather | Monitoring Large-Scale HPC Systems: Data Analytics and Insights    | Ballroom E      |

| 5:30pm-7pm    | Birds of a Feather | OpenACC API 2.5: User Experience, Vendor                           | Hilton Salon C  |

|               |                    | Reaction, Relevance and Roadmap                                    |                 |

| 5:30pm-7pm    | Birds of a Feather | Paving the way for Performance on Intel® Knights Landing Processor | 18AB            |

|               |                    | and Beyond: Unleashing the Power of Next-Generation                |                 |

|               |                    | Many-Core Processors                                               |                 |

| 5:30pm-7pm    | Birds of a Feather | PBS Community: Successes and Challenges in                         | Hilton 410      |

|               |                    | HPC Job Scheduling and Workload Management                         |                 |

| 5:30pm-7pm    | Birds of a Feather | Power API for HPC: Standardizing Power Measurement and Control     | 13A             |

| 5:30pm-7pm    | Birds of a Feather | Software Engineering for Computational Science                     | Hilton 408      |

|               |                    | and Engineering on Supercomputers                                  |                 |

| 5:30pm-7pm    | Birds of a Feather | The Green500 List and its Continuing Evolution                     | 16AB            |

| 5:30pm-7pm    | Birds of a Feather | Towards Standardized, Portable and Lightweight                     | 19AB            |

|               |                    | User-Level Threads and Tasks                                       |                 |

| 5:30pm-7pm    | Birds of a Feather | Two Tiers Scalable Storage: Building POSIX-Like                    | Hilton Salon A  |

|               |                    | Namespaces with Object Stores                                      |                 |

| 5:30pm-7pm    | Birds of a Feather | U.S. Federal HPC Funding and Engagement                            | Hilton Salon D  |

|               |                    | Opportunities                                                      |                 |

|  | THURSD# | Y. NOV | EMBE | R 19 |

|--|---------|--------|------|------|

|--|---------|--------|------|------|

| IIIONODA        | , NOVEMBER 13          |                                                                            |                 |

|-----------------|------------------------|----------------------------------------------------------------------------|-----------------|

| Time            | Event Type             | Session Title                                                              | Location        |

| 8:30am-10am     | Invited Talks          | Plenary Invited Talks Session 6                                            | Ballroom D      |

| 8:30am-5pm      | Posters                | Research & ACM SRC Posters                                                 | Level 4 -Lobby  |

| 9am-5:30pm      | Emerging Technologies  | Emerging Technologies Exhibits                                             | 14              |

| 10am-10:30am    | Tech Program           | Refreshment Break                                                          | Level 4 -Lobby  |

| 10:30am-11:30am | Paper                  | Sampling in Matrix Computations                                            | 18CD            |

| 10:30am-11:30am | Awards Presentation    | ACM Gordon Bell Finalists II                                               | 17AB            |

| 10:30am-12pm    | Paper                  | Programming Tools                                                          | 18AB            |

| 10:30am-12pm    | Paper                  | Resource Management                                                        | 19AB            |

| 10:30am-12pm    | Birds of a Feather     | A Cohesive, Comprehensive Open Community HPC Software Stack                | 15              |

| 10:30am-12pm    | Birds of a Feather     | Variability in Large-Scale, High-Performance Systems                       | 13B             |

| 10:30am-12pm    | Doctoral Showcase      | Doctoral Showcase                                                          | Ballroom E      |

| 10:30am-12pm    | Exhibitor Forum        | Moving, Managing and Storing Data                                          | 12AB            |

| 10:30am-12pm    | HPC for Undergraduates | Careers in HPC                                                             | Hilton 404      |

| 10:30am-12pm    | Invited Talks          | Invited Talks Session 7                                                    | Ballroom D      |

| 10:30am-12pm    | Panel                  | Asynchronous Many-Task Programming Models                                  | 16AB            |

|                 |                        | for Next Generation Platforms                                              |                 |

| 12:15pm-1:15pm  | Awards Presentation    | Award Ceremony                                                             | Ballroom D      |

| 12:15pm-1:15pm  | Birds of a Feather     | Charm++ and AMPI: Adaptive and Asynchronous                                | 13B             |

|                 |                        | Parallel Programming                                                       |                 |

| 12:15pm-1:15pm  | Birds of a Feather     | Charting the PMIx Roadmap                                                  | 15              |

| 12:15pm-1:15pm  | Birds of a Feather     | CSinParallel.org : Update and Free Format Review                           | 18AB            |

| 12:15pm-1:15pm  | Birds of a Feather     | EMBRACE: Toward a New Community-Driven                                     |                 |

|                 |                        | Workshop to Advance the Science of Benchmarking                            | 18CD            |

| 12:15pm-1:15pm  | Birds of a Feather     | Identifying a Few, High-Leverage Energy-Efficiency Metrics                 | 19AB            |

| 12:15pm-1:15pm  | Birds of a Feather     | Recruiting Non-Traditional HPC Users:                                      | 13A             |

|                 |                        | High-Performance Communications for HPC                                    |                 |

| 12:15pm-1:15pm  | Birds of a Feather     | Reproducibility of High Performance Codes and                              | 17AB            |

|                 |                        | Simulations – Tools, Techniques, Debugging                                 |                 |

| 12:15pm-1:15pm  | Birds of a Feather     | Slurm User Group Meeting                                                   | 16AB            |

| 1pm-3:30pm      | HPC Impact Showcase    | HPC Impact Showcase - Thursday                                             | 12AB            |

| 1:30pm-3pm      | Birds of a Feather     | Analyzing Parallel I/O                                                     | 13B             |

| 1:30pm-3pm      | Birds of a Feather     | Impacting Cancer with HPC: Opportunities and Challenges                    | 15              |

| 1:30pm-3pm      | Birds of a Feather     | Scalable <i>In Situ</i> Data Analysis and Visualization Using VisIt/Libsim | 13A             |

| 1:30pm-3pm      | Doctoral Showcase      | Doctoral Showcase                                                          | Ballroom E      |

| 1:30pm-3pm      | Panel                  | Towards an Open Software Stack for Exascale Computing                      | 16AB            |

| 1:30pm-3pm      | Paper                  | Graph Algorithms and Benchmarks                                            | 18CD            |

| 1:30pm-3pm      | Paper                  | Resilience                                                                 | 19AB            |

| 1:30pm-3pm      | Paper                  | State of the Practice: Measuring Systems                                   | 18AB            |

| 3pm-3:30pm      | Tech Program           | Refreshment Break                                                          | Level 4 - Lobby |

### **THURSDAY, NOVEMBER 19**

| Time          | Event Type         | Session Title                                                                                                                               | Location                                                                  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 3:30pm-4:30pm | Paper              | Tensor Computation                                                                                                                          | 18CD                                                                      |

| 3:30pm-5pm    | Birds of a Feather | NSF Big Data Regional Innovation Hubs                                                                                                       | 15                                                                        |

| 3:30pm-5pm    | Birds of a Feather | Taking on Exascale Challenges: Key Lessons and International Collaboration Opportunities Delivered by European Cutting-Edge HPC Initiatives | 13A                                                                       |

| 5:30pm-7pm    | Birds of a Feather | HPC Systems Engineering, Administration and Organization                                                                                    | 13B                                                                       |

| 3:30pm-5pm    | Doctoral Showcase  | Doctoral Showcase                                                                                                                           | Ballroom E                                                                |

| 3:30pm-5pm    | Panel              | Procuring Supercomputers: Best Practices and Lessons Learned                                                                                | 16AB                                                                      |

| 3:30pm-5pm    | Paper              | Power-Constrained Computing                                                                                                                 | 19AB                                                                      |

| 3:30pm-5pm    | Paper              | Programming Systems                                                                                                                         | 18AB                                                                      |

| 6pm-9pm       | Social Event       | Technical Program Conference Reception                                                                                                      | The University of Texas at<br>Austin - Texas Memorial<br>Football Stadium |

### **FRIDAY, NOVEMBER 20**

| TRIBAT, NOVEMBER 20 |                 |                                                              |                  |  |

|---------------------|-----------------|--------------------------------------------------------------|------------------|--|

| Time                | Event Type      | Session Title                                                | Location         |  |

| 8:30am-10am         | Panel           | HPC Transforms DoD, DOE and Industrial Product Design,       | 16AB             |  |

|                     |                 | Development and Acquisition                                  |                  |  |

| 8:30am-10am         | Panel           | Return of HPC Survivor: Outwit, Outlast, Outcompute          | 17AB             |  |

| 8:30am-12pm         | Workshop        | HUST2015: Second International Workshop                      | Hilton Salon B   |  |

|                     |                 | on HPC User Support Tools                                    |                  |  |

| 8:30am-12pm         | Workshop        | NRE2015: Numerical Reproducibility at Exascale               | Hilton 400-402   |  |

| 8:30am-12pm         | Workshop        | Producing High Performance and Sustainable                   | Hilton 408       |  |

|                     |                 | Software for Molecular Simulation                            |                  |  |

| 8:30am-12pm         | Workshop        | SE-HPCCSE2015: Third International Workshop                  | Hilton Salon A   |  |

|                     |                 | on Software Engineering for HPC in Computational             |                  |  |

|                     |                 | Science and Engineering                                      |                  |  |

| 8:30am-12pm         | Workshop        | Software Defined Networking (SDN) for Scientific Networking  | Hilton Salon D   |  |

|                     |                 | Scientific Networking                                        |                  |  |

| 8:30am-12pm         | n-12pm Workshop | VPA2015: Second International Workshop on Visual             | Hilton 410       |  |

|                     |                 | Performance Analysis                                         |                  |  |

| 8:30am-12pm         | Workshop        | WHPCF2015: Eighth Workshop on High Performance Computational | Hilton 406       |  |

|                     |                 | Finance                                                      |                  |  |

| 8:30am-12pm         | Workshop        | Women in HPC: Changing the Face of HPC                       | Hilton 412       |  |

| 10am-10:30am        | Workshop        | Refreshment Break                                            | Hilton 4th Floor |  |

| 10:30am-12pm        | Panel           | HPC and the Public Cloud                                     | 17AB             |  |

| 10:30am-12pm        | Panel           | In Situ Methods: Hype or Necessity?                          | 16AB             |  |

|                     |                 |                                                              |                  |  |

## Plenary/Keynote/ Invited Talks

### **Plenary Talk**

**Monday, November 16**

#### **HPC Matters**

5:30pm-6:30pm Room: Ballroom DEFG

### **Fueling the Transformation**

Diane Bryant (Intel Corporation)

In this lively and entertaining presentation, the audience will experience a visually powerful collection of proof points along with a thought-provoking, forward-looking glimpse of the importance of HPC on several areas of socioeconomic impact.

Join Intel's Senior Vice President, Diane Bryant, as she interacts with multiple industry luminaries for this engaging stage event. During this opening plenary discussion, the audience will be taken on a journey designed to give a deep appreciation for the accomplishments attributed to HPC affecting all of us today, along with an insightful discussion on how HPC will continue to evolve—and continue to change the way we live.

Bryant draws from her experience as Intel's former CIO, her experience in driving the strategic direction of Intel's \$14 billion dollar Data Center Group which includes the company's worldwide HPC business segment, and her passion and commitment for diversity programs – a topic of priority for the SC conference and the global HPC community.

Don't miss this powerful opening plenary session that gets to the very heart of "Why HPC Matters."

**Bio:** Diane M. Bryant is senior vice president and general manager of the Data Center Group for Intel Corporation. Bryant leads the worldwide organization that develops the data center platforms for the digital services economy, generating more than

\$14 billion in revenue in 2014. In her current role, she manages the data center P&L, strategy and product development for enterprise, cloud service providers, telecommunications, and high-performance computing infrastructure, spanning server, storage, and network solutions. Bryant is building the foundation for continued growth by driving new products and technologies—from high-end co-processors for supercomputers to high-density systems for the cloud, to solutions for big data analytics. Previously, Bryant was corporate vice president and chief information officer of Intel. She was responsible for the corporate-wide information technology solutions and services that enabled Intel's business strategies for growth and efficiency. Bryant received her bachelor's degree in electrical engineering from U.C. Davis in 1985 and joined Intel the same year. She attended the Stanford Executive Program and holds four U.S. patents.

### Keynote

### **Tuesday, November 17**

Chair: William Kramer (University of Illinois at

Urbana-Champaign)

8:30am-10am

Room: Ballroom DEFG

### Getting Beyond a Blind Date with Science: Communicating Science for Scientists

Alan Alda (Science Advocate and Emmy Award Winning Actor)